Sunday, July 18, 2010

Pulse Oximeter project continued

You can follow the progress of that project at:

http://pulseoxwireless.blogspot.com/

Tuesday, June 8, 2010

Heart Beat and SpO2 detection

Friday, June 4, 2010

Clock Timing nightmare

Sunday, May 23, 2010

Non overlapping Clock generator

Saturday, May 15, 2010

TIA status and Software Update

PGA Simulation LabVIEW

A simulation was run to mimic the future role of our software. Having implemented DC detection we can now determine the DC bias from the ADC. In the future this software must be able to detect the DC bias and attempt to remove it by writing dynamic software to control the DACs. In addition the software must be able to detect the peak-to-peak signal amplitude and reason how to provide gain. Gain is provided by using a Programmable Gain Amplifier (PGA) to provide gain in steps.

The first simulation ran demonstrated what the PGA will do. A sine function with a random AC amplitude (0 to 100mV) was generated. I then built a stage capable of detecting the peak-to-peak AC amplitude. I then used a for loop to run through each PGA options (1, 2, 5, 10, 20, etc.) to check if the signal was above 5 volt. If the signal was less than 5 volt then it is selected as the true PGA. In the figure below you will see operation of several different simulations. As you can see, with different random AC amplitude the gain is dynamically modified.maximum dynamic range of the signal would be 5 v.

The simulation below show the response of the simulation to different initial signal AC amplitudes. As can be seen, a smaller AC amplitude will allow a higher gain value.

Sunday, May 2, 2010

PGA Simulation Sunday Update

1) As for the randomness of the amplitude of the signal, I have a bit of code in there that provides randomness, although is not hooked up to the sine wave just yet.

a) My first question about it, is that it is giving me integers, and I am not all that great with the types, so I am wondering if there is a way to make it do decimal values rather than U32 values.

b)My second question is that when I attach it to the amplitude, I need a way to have it pick a random number only once rather than constantly changing the amplitude. I am not sure how to do this. I am thinking of using a loop to only make it grab one of the random values, but still am uncertain of how.

2) The sine wave seems to be a nice wave right now. It was a bit tricky for me to get the max and min working, although, it does give me max and min values of y and x separately, which is neat, (i.e. ymin and ymax and xmin and xmax). This is really useful.

a) I have used this to my advantage of taking the ymax and using logic to see if it falls within a range of values (right now I have it set in a range of 4.75 to 5 V, which will likely need to be changed later so there is less error.) With this being said, when it is true, it goes to a true/false case where true does nothing and false has logic further asking if the value was less than 4.75 V, and I would like this to multiply by a particular number to act as the PGA does, so in the first case, multiply by 2. I have the ymax go into this case, but I don't know quite how implement this with having an array of values coming in.

b) The array of values need to be paired back up with the time values. Not certain of how to do this.

c) Of course, with each trial check through the PGA, the gain (or number multiplied by will need to change). Again, I think that this is some sort of loop where i increments (maybe for loop), but I need help on figuring the increment portion.

3) I have not looked at the implementation of adding a DC value for smaller adjustments just yet. Also, it can be noted that for now, the signal is starting out at 2.5 V as it would be assuming that the DC finder was working at this stage.

During lab, I will meet with my team and see what advice they have. Hopefully by the end of lab, there will be a running PGA simulation that fully works.

Monday, April 26, 2010

Progress Report Update

Saturday, April 24, 2010

DC Block Digital Filter Simulations

Sunday, April 18, 2010

Further Discussion on Software

Problem statement #1: The ADC will take in an input signal, which will be analyzed. In the computer analysis, the signal will have an AC signal riding on a DC value. This exact DC value must be subtracted out, so that the signal sits on 0 V DC. This is important so that later in the system, the signal can be biased to 2.5 V allowing for the signal to swing in a dynamic range of 0-5 V. Build a program that allows the computer to calculate this DC value and is able to increment or decrement the DC value in order to have the signal sitting at 0 V DC.

Problem statement #2: As mentioned above, this signal will eventually be biased at 2.5 V. The signal then needs to use the PGA, or programmable gain amplifier to adjust it automatically to swing from 0-5 V, without having saturation.

Problem statement #3: Included above is our thoughts in having need for operating all 4 DACs and eventually operating them solely with the computer and no user input interface. This is another challenge to overcome.

Team Sierra is making progress in software situation, and most importantly identifying what the problems to overcome are. Before implementing ideas, it is important to explore the potential problems and come up with solutions to those problems. For example, it may be easy enough to identify a DC value from knowing the maximum and minimum values from peak to peak of our signal range. We would need to take a sample that would be inserted in an array to allow us to do this. However, we would also have to take into account where the minimum DC value starts from. We may find the DC value from peak to peak to be 1.5 V, although the minimum value may be sitting at 0.5 V to begin with. We must be careful for troublesome points such as this. In dealing with the gain, we must decide whether the computer program will be allowed to saturate before it decides that it needs to go back one gain setting. We must make careful adjustments to the PGA. All different scenarios must be considered.

LABVIEW control

Saturday, April 17, 2010

Trans impedance progress

Thursday, April 15, 2010

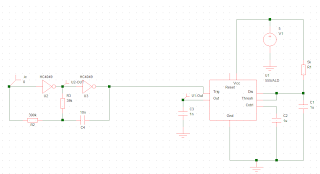

EEC136 LED Driver and Trans impedance update

Wednesday, April 14, 2010

Class Discussion: Clock Timing

Monday, April 12, 2010

LED Driver

Monday, April 5, 2010

Photo diode and Transimpedance update

The function generator was used to drive the LED’s at a specified frequency. The top of the LED was placed above the photodiode and mounted. In this manner, the output the response of the photodiode could be analyzed and quantized.

First, DC measurements were made on the constructed circuit. The diode had an open circuit voltage of around 650 mV. When the circuit was constructed with the 300k resistor though, the voltage across the diode dropped to around 280 mV. This suggests a current of a current of 88 uA. Next, the output of the photodiode was connected to the oscilloscope. I drove the LED with a square wave and observed the waveform at the photodiode output.

One thing I noticed was that an ambient light condition, a large DC bias exists. If the box was isolated and put in the dark box, then the Bias was removed. Additionally, the signal became much less noisy and clearly resembled the driving signal. Another thing I noticed was how the modulation scheme developed. The output LED’s are 180 out of phase and are switched. The switching procedure acts as a modulator shifting cardiac signal from baseband to the carrier band. In this manner, our previous circuit with high pass filter followed by Sample and Hold implements the demodulation application.

I also started looking into the topology selection for transimpedance stage. The reason for a differential stage is to eliminate common mode (CM) noise. I will update with some more information in a later blog. Below is some information on differential opamp stage extracted from Wikipedia. The key idea with this circuit is to amplify the difference between the terminals of diode.

In my next experiments, I will be implementing the transimpedance stage and analyze the approach to remove common mode noise. Additionally, I want to perform some quantization on how hard we can drive the LED’s. As we are driving the LED’s with PWM approach we can increase current through device.

Photodiode/Transimpedance Links

1. Photodiode Technical Information

http://sales.hamamatsu.com/assets/applications/SSD/photodiode_technical_information.pdf

2. Photodiode Characteristics

http://www.optics.arizona.edu/Palmer/OPTI400/SuppDocs/pd_char.pdf

3. Designing of Photodiode Amplifier circuits with OPA128

http://focus.ti.com/lit/an/sboa061/sboa061.pdf

4. OPA350 Datasheet

http://users.ece.utexas.edu/~valvano/Datasheets/OPA4350.pdf

5. Differential Operational Amplifier explanation

http://www.ecircuitcenter.com/Circuits/opdif/opdif.htm

6. Differential Operational Amplifier Stage

http://en.wikipedia.org/wiki/Operational_amplifier_applications